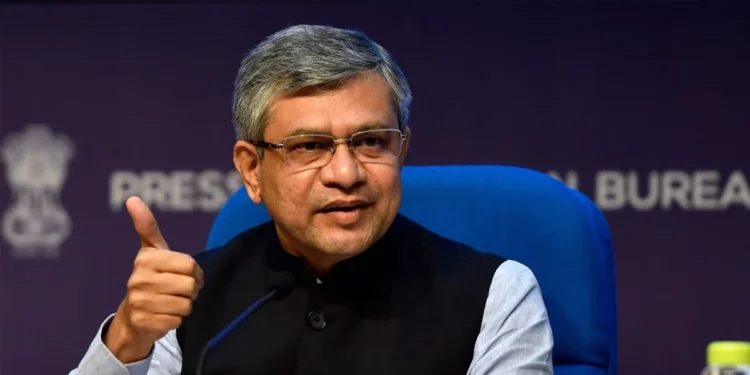

Blitz Bureau

NEW DELHI: India has made major progress toward its target of training 85,000 semiconductor design engineers under the Chips to Startups (C2S) initiative, Union Minister Ashwini Vaishnaw said on March 7. He highlighted the government’s push to strengthen talent development in the semiconductor sector.

The programme, which is part of the India Semiconductor Mission (ISM), focuses on training, upskilling and workforce development to build a robust talent pipeline for the country’s emerging chip ecosystem. Vaishnaw said progress has already been made within the first four years of the 10-year C2S initiative.

“World-class Electronic Design Automation (EDA) tools from global technology companies such as Synopsys, Cadence Design Systems, Siemens, Renesas Electronics, Ansys and AMD have been made available across 315 academic institutions in India,” Vaishnaw said. According to him, these tools allow students to gain practical experience in semiconductor chip design.

The chips designed by students are being fabricated and tested at the Semiconductor Laboratory (SCL), Mohali, giving them hands-on experience across the entire process — from design to fabrication, packaging and testing.

Vaishnaw added that the initiative has grown into the world’s largest open-access EDA programme, with more than 1.85 crore hours of EDA tool usage recorded so far for chip design training. Students from institutions across the country, from Assam to Gujarat and from Jammu and Kashmir to Tamil Nadu, are now actively participating in semiconductor design activities, he said.